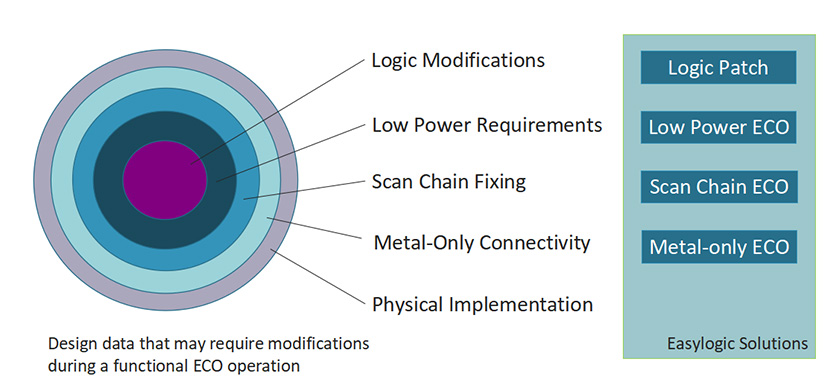

The patch logic creation process begins with making RTL changes. These RTL modifications have ripple effects across functional verification, timing delays, DFT (design-for-test), and metal connectivity. Easy-Logic provides a robust solution that produces the smallest patch logic and optimizes affected design areas downstream.

EasylogicECO streamlines the process from RTL modifications to metal-only post-layout changes by generating minimal patch logic, utilizing spare resources for efficient P&R implementation and seamless timing closure.

Easy-Logic's fully automatic ECO solution utilizes patented technology to help the design team complete the ECO task effortlessly. The short turnaround time also allows the design team to explore different RTL coding methods and ultimately find the optimal ECO results.

The key to success lies in preserving the existing design netlist as much as possible while applying the smallest patch. EasylogicECO adheres to this core principle, ensuring design integrity and minimizing disruption. This approach saves time and resources while delivering reliable results.

-

Patch Logic Generation

-

Post-Layout Functional ECO

A post-layout ECO, also known as metal-only ECO, involves making changes to a layout design that is either near completion or already signed off. Easylogic physical-aware solution generates highly optimized ECO patches, enabling smooth P&R closure with changes to a minimal number of metal layers.

-

Scan Chain Repair

DFT changes are crucial to the success of functional ECO. Since scan chain logic is automatically generated by DFT tools, designers often need to invest significant effort in handling scan chain changes to avoid any loss of DFT coverage. EasylogicECO automatically revises the scan chain netlist to meet the test requirements of the updated design.

Across all three major processes highlighted above, Easylogic solutions provide users with the following benefits:

-

Generating the Smallest Patch

The Easylogic solution employs a specialized optimization algorithm designed to adapt the required logic function to the existing netlist. It begins with meticulously tracing the original netlist to identify the optimal ECO points where design modifications should be made.

Furthermore, the solution provides extensive constraint options, allowing users to specify various design requirements with precision. This combination of innovative tracing, optimization capabilities, and customizable constraints enables Easylogic to deliver tailored, high-quality results for complex ECO challenges.

-

Short Turnaround Time

The total ECO turnaround time is determined by several key factors: design preparation time, tool runtime, downstream P&R runtime, and result verification time. The ability to generate the smallest patch and highly modulized operations allow Easylogic solution to significantly accelerate the downstream P&R process, enabling swift completion across verifications.

This comprehensive approach ensures that each step of the ECO flow is optimized for both speed and scalability, ultimately reducing overall turnaround time.

-

Seamless Design Flow Integration

Easylogic can be integrated with the user's design flow easily, as long as the tools uses standard input/output format. There's no need to replace any tools, and this plug-and-play integration allows users to maintain their existing investments in the design flow.

Easylogic is designed to help users get up and running quickly. With template-based automatic scripting and comprehensive coverage of all application scenarios, users simply fill out the templates with their design information and launch their Easylogic jobs - no complex setup required.